1 Schaltung

Erstellt: DL6GL, 17.02.2018, letzte Änderung 23.01.2021

| « Klirrarmer Sinusgenerator | TOP | » 2 Realisierung |

1.1 Sinusgenerator

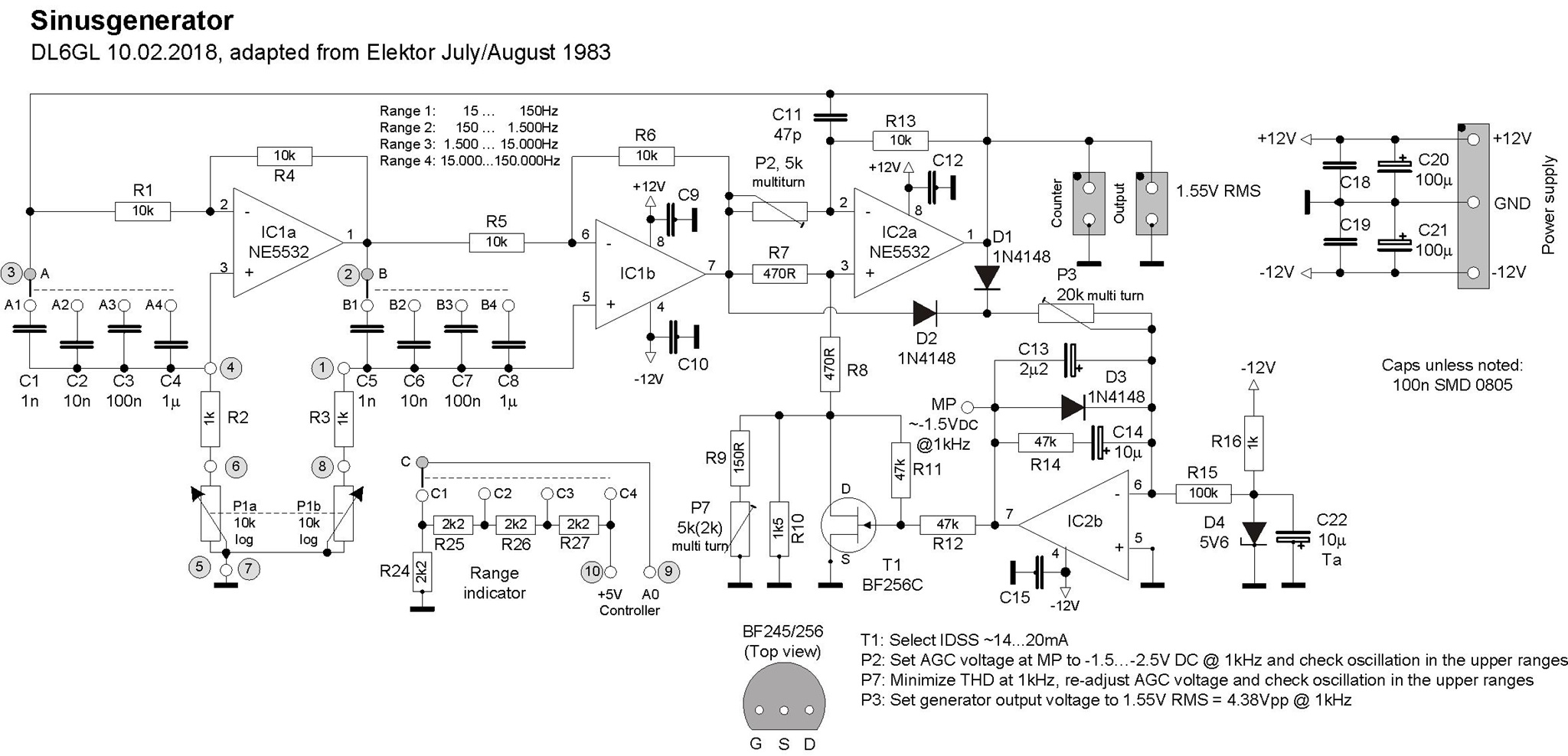

Abb. 1.1: Schaltung des Sinusgenerators.

IC1a, 1b und 2a bilden den eigentlichen Phasenschiebergenerator. Die Schwingfrequenz berechnet sich aus

f0 = 1 / (2πRC), R [Ω], C [F], f0 [Hz]

wobei R für die identischen R2 + P1a und R3 + P1b sowie C für die ebenfalls identischen C1…C4 und C5…C8 stehen. C1 bis C8 sollten jeweils paarweise auf ca. 1% ausgemessen werden. Für C1 und C5, nominal 1nF, sind auf der Schalterplatine jeweils 2 Plätze vorgesehen, um z.B. mit 820pF + x eine Überlappung der beiden oberen Frequenzbereiche herstellen zu können. Mit einem falsch gepolten Stereo Log-Poti ist auch ohne Feintrieb eine halbwegs feinfühlige Frequenzeinstellung möglich. Dabei verringert sich die Frequenz mit Drehung im Uhrzeigersinn. Norbert hat ein lineares Stereo-Poti verwendet, dazu noch einen Feintrieb, siehe Aufmacherbild oben.

Mit den Nominalwerten ergeben sich folgende Einstellbereiche.

| R Min | 1kΩ | f Max |

| R Max | 11kΩ | f Min |

| C | f Min (Hz) | f Max (Hz) |

| 1.000nF | 14 | 159 |

| 100nF | 145 | 1.592 |

| 10nF | 1.447 | 15.915 |

| 1nF | 14.469 | 159.155 |

Für die Resonanzfrequenz f0 bewirken die beiden RC-Glieder eine Phasenverschiebung von je 90°. Die Verstärkungen sind mit R1 + R4 (IC1a) sowie R5 + R6 (IC1b) auf 1 eingestellt. Der invertierende Verstärker IC2a erzeugt weitere 180°, so dass mit insgesamt 360° Phasendrehung zusammen über die mit P2 und R13 einstellbare Verstärkung eine sich aufrechterhaltende Schwingung mit Frequenz f0 einstellt. Am oberen Frequenzende schafft der OpAmp die gewünschte Phasendrehung nicht mehr sauber, so dass mit etwa 100kHz Ende der Fahnenstange ist. Der eher bescheidene Gleichlauf des Stereo-Potis spielt hier auch noch eine Rolle.

Das Ausgangssignal hätte nur eine entfernte Ähnlichkeit mit einem Sinus, wenn nicht für eine Amplitudenregelung gesorgt würde. IC2a arbeitet zugleich über die Dioden D1 und D2 als Vollweggleichrichter. Dessen DC-Spannung vergleicht IC2b mit der von der Zenerdiode D4 gelieferten Referenzspannung. Die Spannungsdifferenz verstärkt IC2b, um damit über die Widerstandsänderung der Drain-Source-Strecke des JFET T1 die Verstärkung von IC2a zu regeln (AGC, automatic gain control). C13 integriert die DC-Spannung, R14 + C14 dämpfen Schwankungen bei Frequenzänderungen und D3 begrenzt positive Ausgangsspannungen zum Gate von T1.

Das bestimmende Element für die Amplitudenregelung ist der JFET T1. Drei Kunstgriffe helfen bei dem an sich nicht ideal linearen Stellglied, das THD in den Griff zu bekommen:

- Die Rückführung des vom nicht invertierenden Eingang von IC2a an der Drain liegenden AC-Signals auf das Gate von T1 mit R11 zusammen mit R12 - je 47kΩ - mit genau der Hälfte des Drainsignals, im Mustergerät 360mVpp zu 180mVpp. Damit werden die geraden Harmonischen unterdrückt, was tatsächlich mit Variation von R11 verifiziert werden konnte. R11 und R12 sollten daher 1%-Typen sein. Soweit sind wir dem Original [1] gefolgt.

- Da geht noch was: Über [1] hinaus haben wir mit dem aus R9, R10 und P7 gebildeten Bypass parallel zur Drain-Source-Strecke den nicht linearen Regelbereich von T1 eingeengt, was eine zusätzliche Reduktion des THD von ca. 0,01% auf ca. 0,005% bei 1kHz zur Folge hatte. Mit P7 wird das THD reduziert. Dabei sind gleichzeitig die Regelspannung am Messpunkt MP und ein sicheres Schwingen in allen Frequenzbereichen zu beachten. Hier ist also ein Kompromiss zwischen Schwingsicherheit und minimal möglichem THD zu finden, siehe Abschnitt 3.

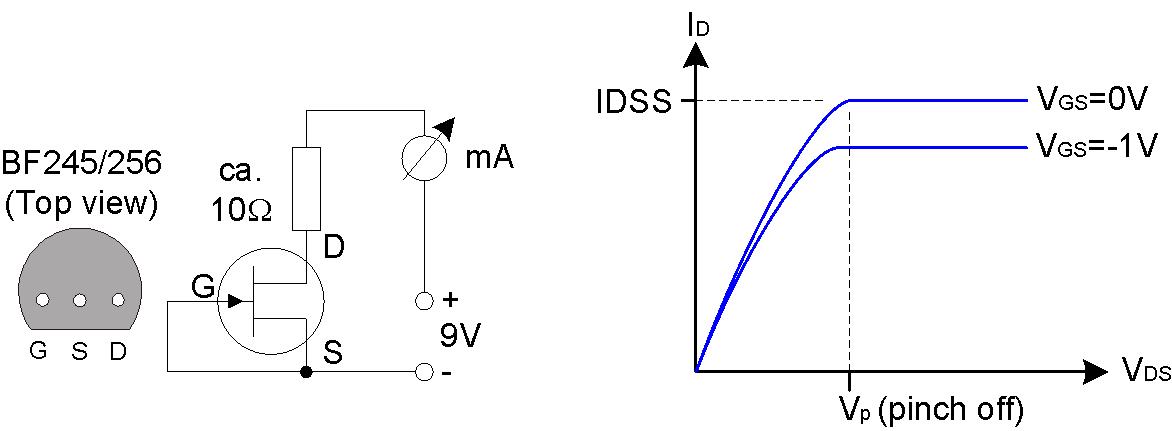

- Einsatz eines selektierten BF256C (bei reichelt.de zu bekommen). FET-Daten streuen beträchtlich. Wir haben aus einer Hand voll BF256C einen mit einem IDSS ~ 15…16mA mit dem Kennlinienschreiber ausgesucht. Es geht auch ohne Kennlinienschreiber (der Drainwiderstand soll eine mögliche Schwingneigung verhindern):

Abb. 1.2: Bestimmung des IDSS mit Bordmitteln.

Am Ausgang von IC2a steht das Sinussignal zur Verfügung.

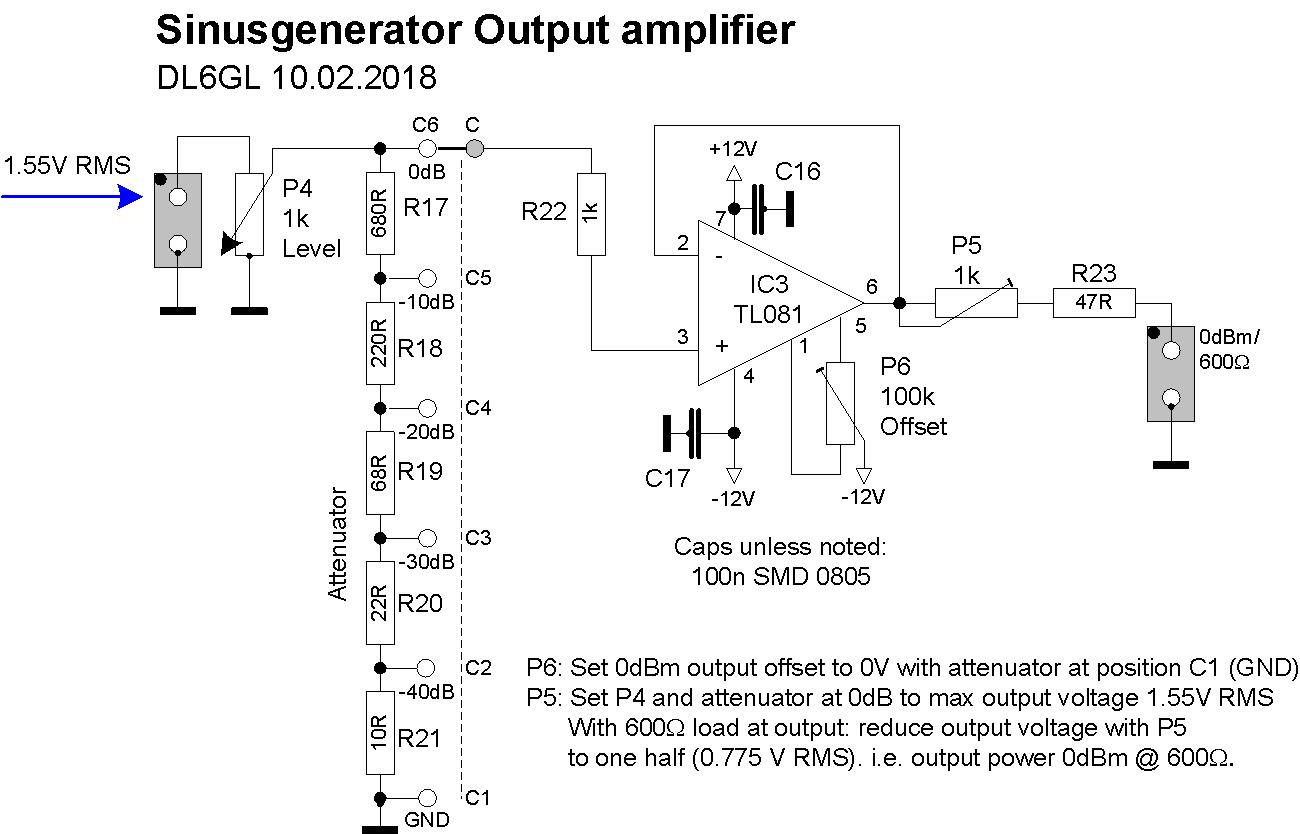

Auf gesonderten Platinen sind ein Stufenabschwächer und ein Spannungsfolger IC3 angeordnet. Mit P6 wird ein DC-Offset kompensiert, mit P5 wird mit einer Last von 600Ω an der Ausgangsbuchse die Ausgangsspannung (1,55V ohne Last) auf genau die Hälfte (775mV) eingestellt. Ausgangsleistung also 0dBm an 600Ω.

Abb. 1.3: Abschwächer und Ausgangsverstärker.

1.2 Digitalteil

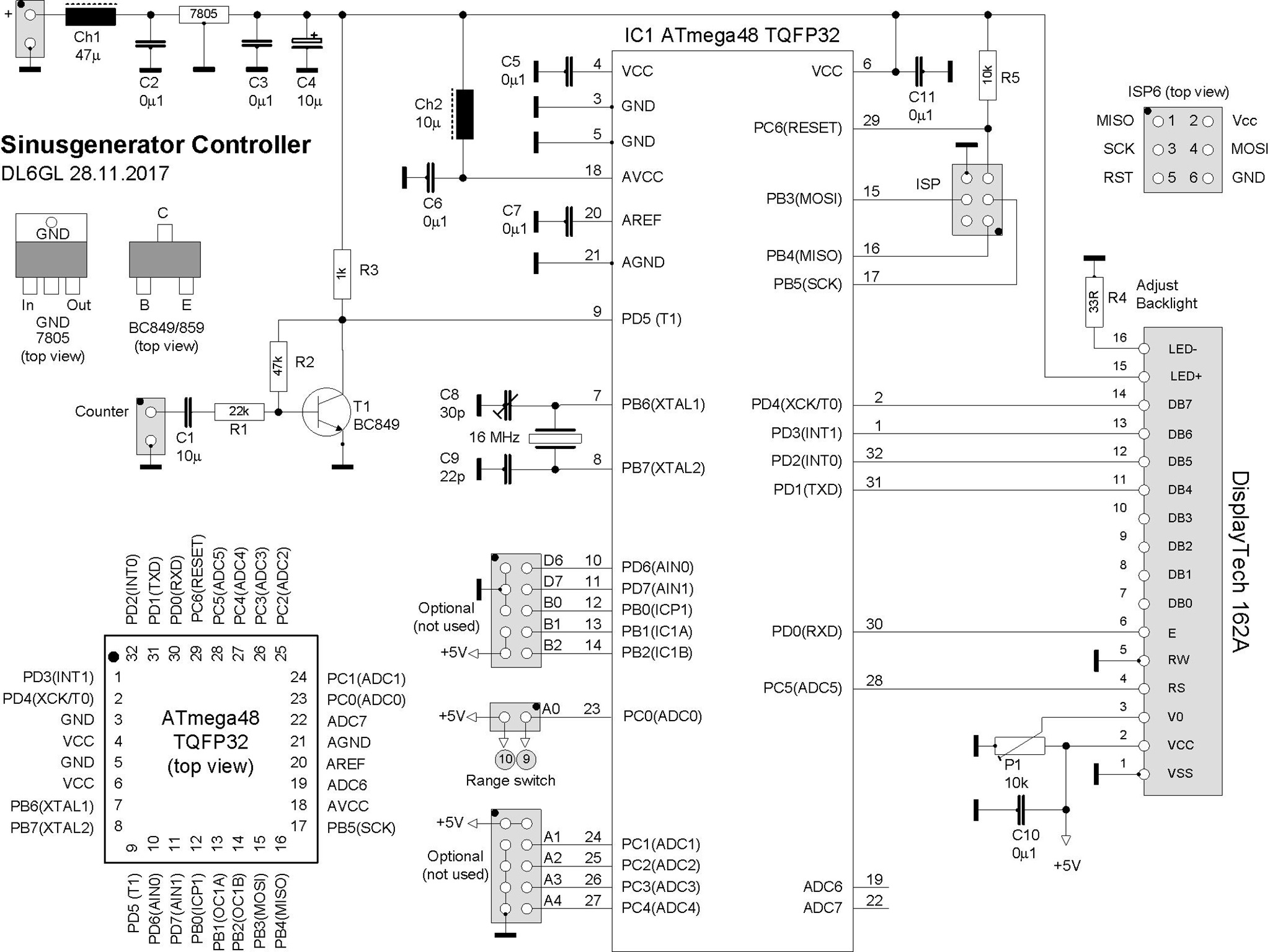

Die Anzeige der eingestellten Frequenz und des Frequenzbereiches besorgt ein ATmega48.

Abb. 1.4: Digitale Frequenzanzeige.

Der Timer/Counter1-Eingang PD5 erhält ein fast digitales Signal von dem mit 1,55VRMS (~ 4,4Vpp) total übersteuerten Transistor T1 zur Zählung. Die Torzeit ist auf 0,5sec eingestellt, so dass sich aus dem mit 2 multiplizierten Zählergebnis eine Frequenzauflösung von 2Hz ergibt. Fallweise kann mit C8 die angezeigte Frequenz justiert werden.

Nachtrag 01/2021: Norbert ist aufgefallen, dass das Ausgangssignal bei Ausgangsamplituden von wenigen Milivolt unsauber auf einem100MHz-Scope erscheinen. Das Signal wird mehrfach getriggert. Bei geringer Bandbreite, etwa 20MHz, ist der Effekt kaum oder nicht zu sehen. Hier koppeln wohl hochfrequenze Störspitzen vom Countereingang des Digitalteils (Abb. 1.4) auf den Ausgang des Analogteils (Abb. 1.1). Abhilfen:

- Abschirmung des Verbindungskabels Analog-Counterausgang zum Digital-Countereingang am Digital-Countereingang abtrennen.

- Entkopplungswiderstand, ca. 22k bis 47k, am Digital-Countereingang in die Verbindung einschleifen. Der Counter muss in allen Frequenzbereichen noch sicher anzeigen.

- Eine bessere Entkopplung wäre wohl mit einem Emitterfolger am Analogausgang mit ggf. noch größerem Entkopplungswiderstand möglich.

Der ADC0-Eingang PC0 erhält vom Range Switch abgestufte Spannungen zur Anzeige des eingestellten Frequenzbereichs.

Mit R4 kann ggf. die Helligkeit der LCD-Hintergrundbeleuchtung eingestellt werden. Mit P1 wird der Anzeigekontrast des LCD justiert.

Da der 5V-Spannungsregler die ungeregelte Leerlaufspannung des Trafos zu verkraften hat, ist er mit dem 7805 gemessen am Strombedarf reichlich überdimensioniert.

Die Firmware ist in BASCOM-AVR programmiert, Quelle und .hex im Download.

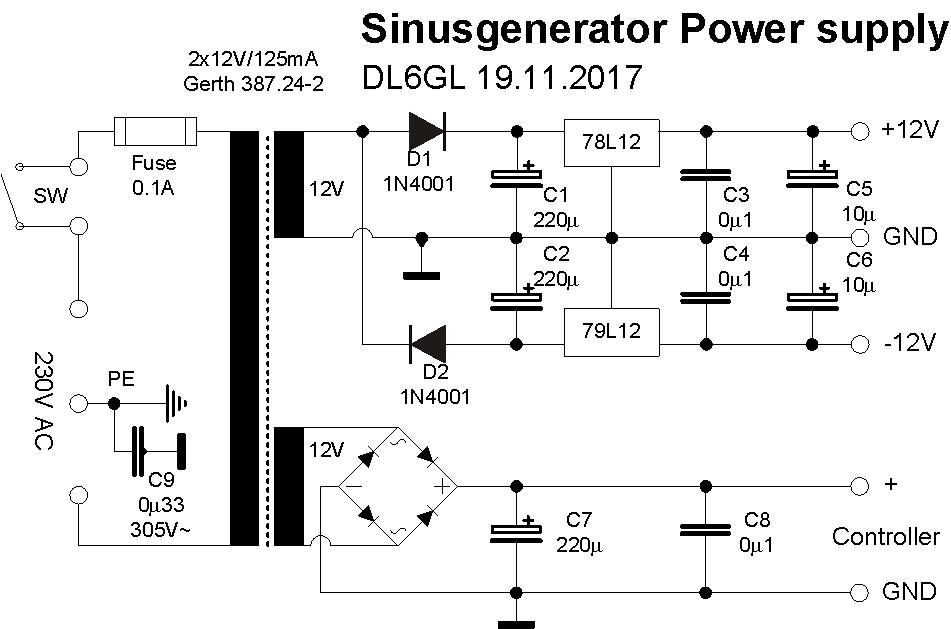

1.3 Netzteil

Abb. 1.5: Netzteil.

| « Klirrarmer Sinusgenerator | TOP | » 2 Realisierung |